Mostrando entradas con la etiqueta electronica digital. Mostrar todas las entradas

Mostrando entradas con la etiqueta electronica digital. Mostrar todas las entradas

sábado, 27 de octubre de 2012

MATERIAL:

2- Resistores de 10k.1- Resistor de 1k.

2- Pushbutton.

1- Led.

1- 7400.

La compuerta NAND se construye para dos entradas A y B , la operación NAND se denota por A'*B'. en términos de la lógica, la compuerta NAND equivale a una compuerta AND seguida por una NOT.

Para construir un retenedor SR las compuertas se acoplan de manera cruzada para obtener la retroalimentación necesaria para formar una red biestable. el retenedor se activa haciendo Q=1 cuando S va de 1 a 0. la función de mantenimiento inicia cuando S regresa a 1. A la inversa, si R va de 1 a 0, el retenedor se desactiva y Q=0.

Simulacion en proteus:

DESCARGAR LA SIMULACION:

http://rapidshare.com/files/3106460427/flip-flop%20sr%20compuertas(nand)%20ROBOTRH.rar

Etiquetas:

descargas,

electronica digital,

practicas simuladas

|

0

comentarios

domingo, 20 de mayo de 2012

MATERIAL:

2- 74LS90.

2-74LS47.

2- Display de 7 segmentos ánodo común.

15- resistores 330 ohms.

1- Compuerta 7414.

1- Led rojo.

2- Pushbutton.

-Bakelita virgen.

-Ácido férrico.

-Hojas para la impresión de circuitos.

DESARROLLO:

74LS90 es un contador.

74LS47 decodificador.

Display 7 segmentos ánodo común.

7414.

CIRCUITO Y SIMULACION EN PROTEUS:

VÍDEO DE LA SIMULACION:

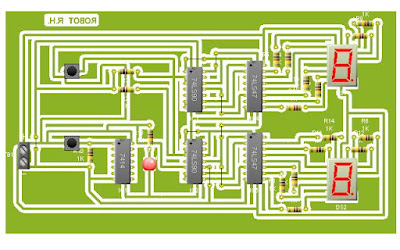

Vista real del circuito.

http://www.mediafire.com/?fnhu8plr7if296j

http://rapidshare.com/files/1250445540/contador_0-99.rar

2- 74LS90.

2-74LS47.

2- Display de 7 segmentos ánodo común.

15- resistores 330 ohms.

1- Compuerta 7414.

1- Led rojo.

2- Pushbutton.

-Bakelita virgen.

-Ácido férrico.

-Hojas para la impresión de circuitos.

DESARROLLO:

74LS90 es un contador.

74LS47 decodificador.

Display 7 segmentos ánodo común.

7414.

CIRCUITO Y SIMULACION EN PROTEUS:

Diagrama del contador 0-99.

PCB:

Vista de impresión.Vista real del circuito.

NOTA: las lineas negras de la vista real del PCB son puentes.

DESCARGAR SIMULACION Y PCB:

http://rapidshare.com/files/1250445540/contador_0-99.rar

Etiquetas:

electronica digital,

proyectos

|

36

comentarios

viernes, 11 de mayo de 2012

VHDL

los lenguajes de descripción de hardware(VHDL) proporcionan medios eficaces para el diseño asistido por computadora(CAD) de redes lógicas digitales. el VHDL es solo un lenguaje de alto nivel que permite describir todas las características importantes de una red lógica de complejidad arbitraria

GAL

matriz lógica genérica (Generic array logic) fueron desarrolladas por Lattice Semiconductor. Una GAL permite implementar cualquier expresión en suma de productos con

un número de variables definidas. El proceso de programación consiste

en activar o desactivar cada celda E2CMOS con el objetivo de aplicar la

combinación adecuada de variables a cada compuerta AND y obtener la suma

de productos.

Las celdas E2CMOS activadas conectan las variables deseadas o sus

complementos con las apropiadas entradas de las puertas AND. Las celdas

E2CMOS están desactivadas cuando una variable o su complemento no se

utiliza en un determinado producto. La salida final de la puerta OR es

una suma de productos. Cada fila está conectada a la entrada de una

puerta AND, y cada columna a una variable de entrada o a su complemento.

Mediante la programación se activa o desactiva cada celda E2CMOS, y se

puede aplicar cualquier combinación de variables de entrada, o sus

complementos, a una puerta AND para generar cualquier operación producto

que se desee. Una celda activada conecta de forma efectiva su

correspondiente fila y columna, y una celda desactivada desconecta la

fila y la columna.

Las celdas se pueden borrar y reprogramar eléctricamente. Una celda

E2CMOS típica puede mantener el estado en que se ha programado durante

20 años o más. Las macroceldas lógicas de salida (OLMCs) están formadas

por circuitos lógicos que se pueden programar como lógica combinacional o

como lógica secuencial. Las OLMCs proporcionan mucha más flexibilidad

que la lógica de salida fija de una PAL.

PROGRAMA UTILIZADO:ispLEVER Classic Software.

Su descarga es gratuita solo se deben registrar.

MATERIAL:

1- Led.

1- Resistor de 220.

6- Pushbutton.

6- Resistores de 10k.

Programa en vhdl:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity mux41 is

port(

sel: in std_logic_vector ( 1 downto 0 ); //sel se describe de dos bits

e1: in std_logic ;

e2: in std_logic ;

e3: in std_logic ;

e4: in std_logic ;

sal: out std_logic );

end;

architecture behavioral of mux41 is

begin

process(e1,e2,e3,e4,sel)

begin

case sel is

when "00"=>sal<=e1;

when "01"=>sal<=e2;

when "10"=>sal<=e3;

when "11"=>sal<=e4;

when others=>null;

end case;

end process;

end behavioral;

Configuracion de entradas y salidas del gal (lo arroja el programa).

Funcionamiento:

sel_0=0 y sel_1= 0 la sal es = e1.

sel_0=1 y sel_1= 0 la sal es = e2.

sel_0=0 y sel_1= 1 la sal es = e3.

sel_0=1 y sel_1= 1 la sal es = e4.

Despues de compilar el programa se simulo en proteus.

Para simularlo en proteus dar doble clic en el gal y buscar el archivo .jed que esta en la carpeta gal del archivo que van a bajar.

Circuito en proteus.

Condición sel_0=0 sel_1=0 la sal = E1.

Condición sel_0=1 sel_1=1 la sal =E4.

Descarga de archivo con simulacion y programa en vhdl:

Etiquetas:

electronica digital,

practicas simuladas,

vhdl

|

0

comentarios

lunes, 23 de abril de 2012

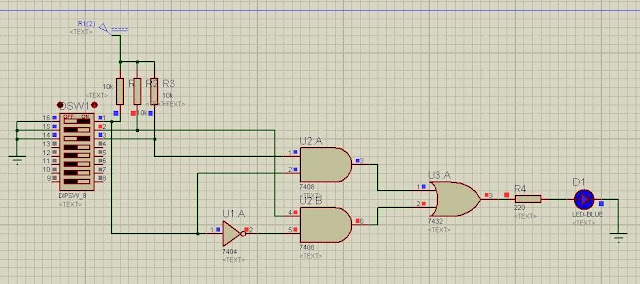

El mux 4-1.

Se selecciona la salida dependiendo la combinacion:

A=0 y B=0 la salida depende de D1.

A=1 y B=0 la salida depende de D2.

A=0 y B=1 la salida depende de D3.

A=1 y B=1 la salida depende de D4.

Simulacion:

Para manipular A y B debe activarse o desactivarse el canal 8(B) y 7(A) de DIPSW para manipular

D1(9), D2(10), D3(11) y D4(12) del DIPSW.

La imagen muestra que al estar A=0 y B=1 la salida depende de D3(11) del DIPSW y como esta en uno la salida esta en uno.

MATERIAL:

1- 7404 (compuerta NOT).

2- 7411(AND de 3 entradas).

1-4272(OR de 4 entradas).

1-DIPSW de 6.

6-resistencias de 1k (café, negro, rojo).

1-resistencia de 330 (naranja, naranja, café) se pone en el led de la salida.

1-led.

DESCARGAR SIMULACION:

Se selecciona la salida dependiendo la combinacion:

A=0 y B=0 la salida depende de D1.

A=1 y B=0 la salida depende de D2.

A=0 y B=1 la salida depende de D3.

A=1 y B=1 la salida depende de D4.

Simulacion:

Para manipular A y B debe activarse o desactivarse el canal 8(B) y 7(A) de DIPSW para manipular

D1(9), D2(10), D3(11) y D4(12) del DIPSW.

La imagen muestra que al estar A=0 y B=1 la salida depende de D3(11) del DIPSW y como esta en uno la salida esta en uno.

MATERIAL:

1- 7404 (compuerta NOT).

2- 7411(AND de 3 entradas).

1-4272(OR de 4 entradas).

1-DIPSW de 6.

6-resistencias de 1k (café, negro, rojo).

1-resistencia de 330 (naranja, naranja, café) se pone en el led de la salida.

1-led.

DESCARGAR SIMULACION:

Etiquetas:

electronica digital,

practicas simuladas

|

1 comentarios

viernes, 23 de diciembre de 2011

Diagrama de un mux2-1, básicamente la lógica es seleccionar la entrada que queremos para que esta sea la salida.

A(0)=OUT(0).

A(1)=OUT(1).

Si SEL(1) entonces sera B(OUT).

B(0)=OUT(0).

B(1)=OUT(1).

En la siguiente figura se muestra la simulación en proteus.

Material:

1-Dip switch 8p.

3-Resistencias de 10k.

1-.Resistencia de 220.

1- Led.

1-Fuente de alimentacion de 5v.

1-7404.

1-7408.

DESCARGAR SIMULACIÓN:

VÍDEO DE LA SIMULACIÓN:

Etiquetas:

electronica digital,

practicas simuladas

|

0

comentarios

Suscribirse a:

Entradas (Atom)

.png)