domingo, 20 de mayo de 2012

MATERIAL:

2- 74LS90.

2-74LS47.

2- Display de 7 segmentos ánodo común.

15- resistores 330 ohms.

1- Compuerta 7414.

1- Led rojo.

2- Pushbutton.

-Bakelita virgen.

-Ácido férrico.

-Hojas para la impresión de circuitos.

DESARROLLO:

74LS90 es un contador.

74LS47 decodificador.

Display 7 segmentos ánodo común.

7414.

CIRCUITO Y SIMULACION EN PROTEUS:

VÍDEO DE LA SIMULACION:

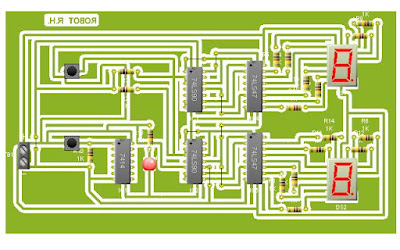

Vista real del circuito.

http://www.mediafire.com/?fnhu8plr7if296j

http://rapidshare.com/files/1250445540/contador_0-99.rar

2- 74LS90.

2-74LS47.

2- Display de 7 segmentos ánodo común.

15- resistores 330 ohms.

1- Compuerta 7414.

1- Led rojo.

2- Pushbutton.

-Bakelita virgen.

-Ácido férrico.

-Hojas para la impresión de circuitos.

DESARROLLO:

74LS90 es un contador.

74LS47 decodificador.

Display 7 segmentos ánodo común.

7414.

CIRCUITO Y SIMULACION EN PROTEUS:

Diagrama del contador 0-99.

PCB:

Vista de impresión.Vista real del circuito.

NOTA: las lineas negras de la vista real del PCB son puentes.

DESCARGAR SIMULACION Y PCB:

http://rapidshare.com/files/1250445540/contador_0-99.rar

Etiquetas:

electronica digital,

proyectos

|

36

comentarios

viernes, 11 de mayo de 2012

VHDL

los lenguajes de descripción de hardware(VHDL) proporcionan medios eficaces para el diseño asistido por computadora(CAD) de redes lógicas digitales. el VHDL es solo un lenguaje de alto nivel que permite describir todas las características importantes de una red lógica de complejidad arbitraria

GAL

matriz lógica genérica (Generic array logic) fueron desarrolladas por Lattice Semiconductor. Una GAL permite implementar cualquier expresión en suma de productos con

un número de variables definidas. El proceso de programación consiste

en activar o desactivar cada celda E2CMOS con el objetivo de aplicar la

combinación adecuada de variables a cada compuerta AND y obtener la suma

de productos.

Las celdas E2CMOS activadas conectan las variables deseadas o sus

complementos con las apropiadas entradas de las puertas AND. Las celdas

E2CMOS están desactivadas cuando una variable o su complemento no se

utiliza en un determinado producto. La salida final de la puerta OR es

una suma de productos. Cada fila está conectada a la entrada de una

puerta AND, y cada columna a una variable de entrada o a su complemento.

Mediante la programación se activa o desactiva cada celda E2CMOS, y se

puede aplicar cualquier combinación de variables de entrada, o sus

complementos, a una puerta AND para generar cualquier operación producto

que se desee. Una celda activada conecta de forma efectiva su

correspondiente fila y columna, y una celda desactivada desconecta la

fila y la columna.

Las celdas se pueden borrar y reprogramar eléctricamente. Una celda

E2CMOS típica puede mantener el estado en que se ha programado durante

20 años o más. Las macroceldas lógicas de salida (OLMCs) están formadas

por circuitos lógicos que se pueden programar como lógica combinacional o

como lógica secuencial. Las OLMCs proporcionan mucha más flexibilidad

que la lógica de salida fija de una PAL.

PROGRAMA UTILIZADO:ispLEVER Classic Software.

Su descarga es gratuita solo se deben registrar.

MATERIAL:

1- Led.

1- Resistor de 220.

6- Pushbutton.

6- Resistores de 10k.

Programa en vhdl:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity mux41 is

port(

sel: in std_logic_vector ( 1 downto 0 ); //sel se describe de dos bits

e1: in std_logic ;

e2: in std_logic ;

e3: in std_logic ;

e4: in std_logic ;

sal: out std_logic );

end;

architecture behavioral of mux41 is

begin

process(e1,e2,e3,e4,sel)

begin

case sel is

when "00"=>sal<=e1;

when "01"=>sal<=e2;

when "10"=>sal<=e3;

when "11"=>sal<=e4;

when others=>null;

end case;

end process;

end behavioral;

Configuracion de entradas y salidas del gal (lo arroja el programa).

Funcionamiento:

sel_0=0 y sel_1= 0 la sal es = e1.

sel_0=1 y sel_1= 0 la sal es = e2.

sel_0=0 y sel_1= 1 la sal es = e3.

sel_0=1 y sel_1= 1 la sal es = e4.

Despues de compilar el programa se simulo en proteus.

Para simularlo en proteus dar doble clic en el gal y buscar el archivo .jed que esta en la carpeta gal del archivo que van a bajar.

Circuito en proteus.

Condición sel_0=0 sel_1=0 la sal = E1.

Condición sel_0=1 sel_1=1 la sal =E4.

Descarga de archivo con simulacion y programa en vhdl:

Etiquetas:

electronica digital,

practicas simuladas,

vhdl

|

0

comentarios

jueves, 3 de mayo de 2012

Esta practica nos indica como utilizar una tabla en el pic 16f84a

Através de la combinacion del puerto b se realizan los números en un display de 7 segmentos(0-7).Tabla de verdad.

A2

|

A1

|

A0

|

B7

|

B6

|

B5

|

B4

|

B3

|

B2

|

B1

|

B0

|

0

|

0

|

0

|

0

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

1

|

1

|

0

|

0

|

1

|

0

|

0

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

0

|

0

|

1

|

1

|

1

|

1

|

1

|

0

|

0

|

0

|

1

|

1

|

0

|

0

|

1

|

1

|

0

|

1

|

0

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

1

|

0

|

0

|

1

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

0

|

0

|

0

|

0

|

0

|

1

|

1

|

1

|

Programa :

status equ 0x03

porta equ 0x05

portb equ 0x06

trisa equ 0x85

trisb equ 0x86

pcl equ 0x02

org 0

inicio

bsf status,5

movlw b'11111'

movwf trisa //configura porta como entrada

clrf trisb //configura portb como salida

bcf status,5

principal

movf porta,w

andlw b'00111' //utilizan los tres bits menos significativos de porta , a0, a1, a2

call tabla //llamado a la subrutina tabla

movwf portb //se muestra el valor de la tabla por el puerto b

goto principal //buncle infinito

tabla

addwf pcl,f //salto indexado(se posiciona en el valor requerido)

retlw b'00111111' // 0

retlw b'00000110' // 1

retlw b'01011011' // 2

retlw b'01001111' // 3

retlw b'01100110' //4

retlw b'01101101' //5

retlw b'01111101' //6

retlw b'00000111' //7

return //retorna a la rutina principal

end

Si porta es 010 addwf se posiciona en la tercera linea (01011011) y rtlw extrae ese dato y se retorna al programa principal el cual muetra el dato seleccionado por el puerto b(movwf portb).

Se pueden realizar todos los números del display de 7 segmentos pero tendríamos que aumentar a 3 para tener mas combinaciones posibles es decir los cuatro bits mas significativos.

.

Circuito en proteus.Combinacion en porta(00001) y se activa en portb(00000110).

Para simular en proteus el pic, abrir la simulacion, dar doble clic en el símbolo del pic, en program file dar clic en la carpeta y seleccionar el .hex de la carpeta que bajaron y configurar en clock frequency 4MHz.

Video de la simulacion:

Video de la simulacion:

Material:

1- Pic 16f84a.

1-Display 7 segmentos cátodo común.

1-Dip switch 4

1-Cristal 4Mhz.

2-Capacitores electroliticos 22pf.

3-Resistencias de 10k.

2-Resistencias de 220 (van en los comunes del display).

DESCARGAR SIMULACION Y PROGRAMA:

Etiquetas:

lenguje asm,

practicas simuladas

|

0

comentarios

Suscribirse a:

Comentarios (Atom)

.png)